Научные открытия приносят практическую пользу лишь после внедрения в производство. А для этого необходима разработка и производство промышленного оборудования, так что вершиной мастерства остаётся изготовление условных производственных станков.

Сегодня такой «станок» для массового производства 3-нм чипов представила американская компания Applied Materials. С его помощью 3-нм техпроцессы Samsung и TSMC станут реальностью.

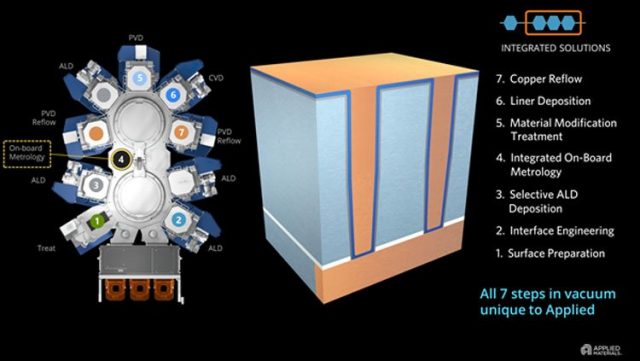

На мероприятии Applied 2021 Logic компания Applied Materials представила установку Endura Copper Barrier Seed IMS. Это система с девятью уникальными модулями (камерами) для поэтапного создания структур на кремнии на 300-мм пластинах для производства микросхем (последовательность обработки показана на видео ниже). Модули создают на кристаллах тонкие плёнки методом осаждения из газовой среды, а также соединены с системой метрологии для контроля толщины и качества слоёв (плёнок).

Установка Endura Copper Barrier Seed IMS решает одну, но важнейшую задачу — создаёт на кристалле соединительные линии для связи всех элементов микросхемы в единую электронную схему. По сути — это прокладка проводки между транзисторами, конденсаторами и резисторами на кристалле, от свойств которой зависит качество, долговечность, потребление и даже размеры микросхем.

Современные чипы состоят из десятков миллиардов соединений, и чем тоньше техпроцесс, тем сильнее они греются. На долю потребления соединений теперь уходит не менее 30 % потребления микросхем. В задачу разработчиков оборудования для изготовления внутричиповых проводников входит необходимость снизить эти потери — уменьшить сопротивление как самих линий, так и мест контакта с полупроводником на кристалле. По словам Applied Materials, новый техпроцесс и материалы установки Endura Copper Barrier Seed IMS значительно снижают сопротивление линий связи и до 50 % уменьшают контактное сопротивление, в чём помогла технология особого оплавления меди для заполнения возможных пустот в месте контакта.

Без всех этих улучшений сопротивление линий связи в чипе при переходе от 7-нм техпроцесса к 3-нм выросло бы в 10 раз. Теперь этого не произойдёт, а оборудование поможет выпускать энергоэффективные чипы не только с использованием 3-нм техпроцесса, но даже с меньшими нормами.

Источник: VentureBeat